Significant increases in application complexity demand processing requirements that exceed the performance achievable by current processors using software only implementations. For example, recent multimedia standards, such as JPEG2000, have significantly increased computational demands compared to previous standards. In an effort to alleviate the cost of developing software and/or hardware solutions capable of fully supporting such standards, many define several profiles — specific settings for various configurable parameters — that reduce the level of complexity needed to implement a specific profile. However, the number and variability of profiles even within a single domain still precludes traditional hardware implementations as a viable option for most applications.

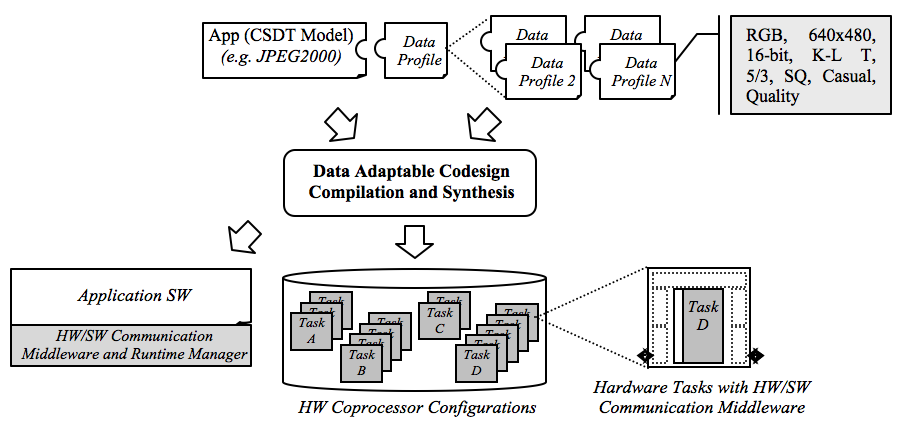

The Data-Adaptable Reconfigurable Embedded Systems (DARES) project focuses on developing hardware/software codesign and reconfigurable computing methodologies driven by data-adaptability. This data-adaptable approach allows designers to directly model data configurability of an application, thereby enabling a solution that can be dynamically reconfigured at runtime based on the profile of incoming data. The DARES project combines modeling techniques for capturing the data configuration space with new hardware/software codesign techniques to synthesize reconfigurable circuits and communication resources directly from the data/application model. The resulting hardware/software implementation provides the flexibility of software with the performance of hardware.

This research was supported by the National Science Foundation (CNS-0915010).